- RISC is a microprocessor architecture that has smaller/simpler set of instructions

- CISC is a microprocessor architecture that has larger/more complex set of instructions

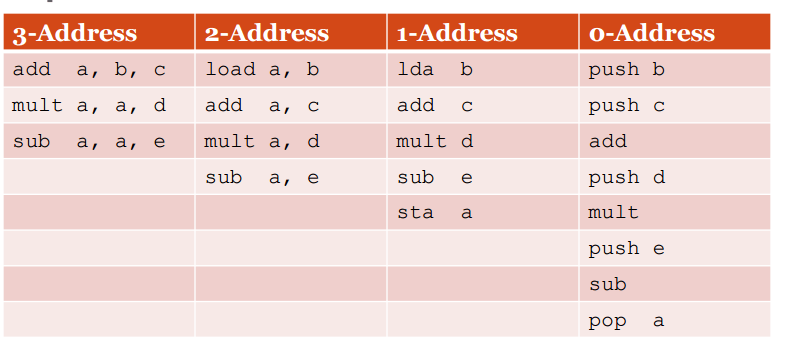

- 3, 2, 1 address machines just mean how many addresses are in an instruction

When first investigating the relationship between RISC vs CISC and n-address machines, with the help of the slide below, I was able to quickly associate 3 address with CISC and 0 address with RISC.  I saw that 3 address instructions were much more complicated than 0 address and therefore would make sense for CISC design. Similar reasoning for 0 address machine and RISC design. How would you make the distinguish for CISC and RISC with the address sizes in the middle – 1 and 2?

I saw that 3 address instructions were much more complicated than 0 address and therefore would make sense for CISC design. Similar reasoning for 0 address machine and RISC design. How would you make the distinguish for CISC and RISC with the address sizes in the middle – 1 and 2?

Asked By : committedandroider

Answered By : Wandering Logic

- Fixed width instructions. Usually 32-bits or 16-bits. This makes it easier for the instruction decoder to find the boundaries between instructions. In CISC machines, by contrast, the different instructions can range in length from 8-bits to as much 64-bits. This makes the job of the instruction decoder somewhat harder in CISC machines, but can result in programs consuming less memory.

- Fewer operand addressing modes. In a RISC machine typically each operator (add, sub, jmp, load) has only one available addressing mode for its operands (the a, b, c, d, and e in your picture.) Typically for arithmetic type instructions (add, sub, xor, …) the only available addressing mode is register direct. The source operands are found in registers, and the result of the computation can only be placed in a register. Load and store type instructions typically have one operand that is register direct and the other operand is register indirect plus offset. Jump and branch type instructions will typically have a target operand that is pc relative. There will typically also be a few jump and branch type instructions with a register indirect target, and sometimes a jump instruction with an absolute target operand. The smaller number of operand addressing modes is typically the only way in which “RISC” instruction sets are actually reduced (compared to “CISC” instruction sets). The reasoning, again, has to do with trying to keep the instruction decoder as simple as possible in RISC machines. The simple operand addressing modes are easier to implement in a simple pipeline, and so the decoder in modern CISC machines often has to do extra work to crack instructions with complex operand modes into sequences of micro-operations that are more like RISC instructions.

- There is a tendency for RISC architectures to have more register names available. Many RISC architectures have 32 registers, while many CISC architectures have only 8 or 16. This again has to do with making it somewhat simpler to exploit instruction-level parallelism with a simple pipeline. Having more available register names makes it possible for the compiler to use different register names for unrelated computations, without requiring the hardware to do register renaming.

- RISC architectures tend to have “3-address” instructions, while CISC architectures tend to have mostly “2-address” instructions. The notion of “3-address” vs. “2-address” is also somewhat fuzzy (and somewhat mis-named). Every add instruction has 3 operands, 2 source operands and 1 destination operand. The real distinction is whether those operands are explicit or implicit. In a so-called “3-address” instruction you make all 3 operands explicit. In a so-called “2-address” instruction you make the destination operand explicit and one of the source operands explicit. The third source operand is implicit: it is always the same address as the destination operand. In a so-called “1-address” instruction only one of the source operands is explicit. The other source operand is implicitly either an accumulator register or the top of the stack, as is the destination operand. Finally in a “0-address” instruction all the operands are implicit (usually the two source operands are the top two values on the stack and the destination goes back on the top of the stack.)

To sum up: these are all marketing terms, and don’t really mean much. The important concepts have to do with the relationship between different instruction-set design choices and how those choices make it easier or harder to implement hardware pipelines.

Best Answer from StackOverflow

Question Source : http://cs.stackexchange.com/questions/43236